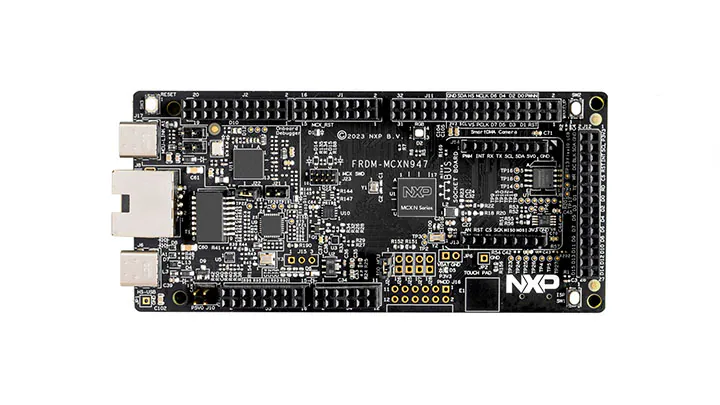

NXP FRDM-MCXN947

Overview

FRDM-MCXN947 are compact and scalable development boards for rapid prototyping of MCX N94 and N54 MCUs. They offer industry standard headers for easy access to the MCUs I/Os, integrated open-standard serial interfaces, external flash memory and an on-board MCU-Link debugger. MCX N Series are high-performance, low-power microcontrollers with intelligent peripherals and accelerators providing multi-tasking capabilities and performance efficiency.

Hardware

MCX-N947 Dual Arm Cortex-M33 microcontroller running at 150 MHz

2MB dual-bank on chip Flash

512 KB RAM

External Quad SPI flash over FlexSPI

USB high-speed (Host/Device) with on-chip HS PHY. HS USB Type-C connectors

10x LP Flexcomms each supporting SPI, I2C, UART

2x FlexCAN with FD, 2x I3Cs, 2x SAI

1x Ethernet with QoS

On-board MCU-Link debugger with CMSIS-DAP

Arduino Header, FlexIO/LCD Header, SmartDMA/Camera Header, mikroBUS

For more information about the MCX-N947 SoC and FRDM-MCXN947 board, see:

Supported Features

The FRDM-MCXN947 board configuration supports the following hardware features:

Interface |

Controller |

Driver/Component |

|---|---|---|

NVIC |

on-chip |

nested vector interrupt controller |

SYSTICK |

on-chip |

systick |

PINMUX |

on-chip |

pinmux |

GPIO |

on-chip |

gpio |

UART |

on-chip |

serial port-polling; serial port-interrupt |

SPI |

on-chip |

spi |

DMA |

on-chip |

dma |

I2C |

on-chip |

i2c |

CLOCK |

on-chip |

clock_control |

FLASH |

on-chip |

soc flash |

FLEXSPI |

on-chip |

flash programming |

DAC |

on-chip |

dac |

ENET QOS |

on-chip |

ethernet |

WATCHDOG |

on-chip |

watchdog |

PWM |

on-chip |

pwm |

CTIMER |

on-chip |

counter |

USDHC |

on-chip |

sdhc |

VREF |

on-chip |

regulator |

ADC |

on-chip |

adc |

USBHS |

on-chip |

USB device |

LPCMP |

on-chip |

sensor(comparator) |

FLEXCAN |

on-chip |

CAN |

LPTMR |

on-chip |

counter |

FLEXIO |

on-chip |

flexio |

DISPLAY |

on-chip |

flexio; MIPI-DBI. Tested with NXP LCD_PAR_S035 TFT LCD Module |

Targets available

The default configuration file boards/nxp/frdm_mcxn947/frdm_mcxn947_mcxn947_cpu0_defconfig only enables the first core.

Other hardware features are not currently supported by the port.

Connections and IOs

The MCX-N947 SoC has 6 gpio controllers and has pinmux registers which can be used to configure the functionality of a pin.

Name |

Function |

Usage |

|---|---|---|

P0_PIO1_8 |

UART |

UART RX |

P1_PIO1_9 |

UART |

UART TX |

System Clock

The MCX-N947 SoC is configured to use PLL0 running at 150MHz as a source for the system clock.

Serial Port

The FRDM-MCXN947 SoC has 10 FLEXCOMM interfaces for serial communication. Flexcomm 4 is configured as UART for the console.

Programming and Debugging

Build and flash applications as usual (see Building an Application and Run an Application for more details).

Configuring a Debug Probe

A debug probe is used for both flashing and debugging the board. This board is configured by default to use the MCU-Link CMSIS-DAP Onboard Debug Probe.

Using LinkServer

Linkserver is the default runner for this board, and supports the factory

default MCU-Link firmware. Follow the instructions in

MCU-Link CMSIS-DAP Onboard Debug Probe to reprogram the default MCU-Link

firmware. This only needs to be done if the default onboard debug circuit

firmware was changed. To put the board in DFU mode to program the firmware,

short jumper J21.

Using J-Link

There are two options. The onboard debug circuit can be updated with Segger

J-Link firmware by following the instructions in

MCU-Link JLink Onboard Debug Probe.

To be able to program the firmware, you need to put the board in DFU mode

by shortening the jumper J21.

The second option is to attach a J-Link External Debug Probe to the

10-pin SWD connector (J23) of the board. Additionally, the jumper J19 must

be shortened.

For both options use the -r jlink option with west to use the jlink runner.

west flash -r jlink

Configuring a Console

Connect a USB cable from your PC to J17, and use the serial terminal of your choice (minicom, putty, etc.) with the following settings:

Speed: 115200

Data: 8 bits

Parity: None

Stop bits: 1

Flashing

Here is an example for the Hello World application.

# From the root of the zephyr repository

west build -b frdm_mcxn947/mcxn947/cpu0 samples/hello_world

west flash

Open a serial terminal, reset the board (press the RESET button), and you should see the following message in the terminal:

*** Booting Zephyr OS build v3.6.0-479-g91faa20c6741 ***

Hello World! frdm_mcxn947/mcxn947/cpu0

Flashing to QSPI

Here is an example for the Hello World application.

west build -b frdm_mcxn947/mcxn947/cpu0/qspi zephyr/samples/hello_world -- -DCONFIG_MCUBOOT_SIGNATURE_KEY_FILE=\"bootloader/mcuboot/root-rsa-2048.pem\" -DCONFIG_BOOTLOADER_MCUBOOT=y

west flash

In order to load Zephyr application from QSPI you should program a bootloader like MCUboot bootloader to internal flash. Here are the steps.

west build -b frdm_mcxn947/mcxn947/cpu0/qspi bootloader/mcuboot/boot/zephyr

west flash

Open a serial terminal, reset the board (press the RESET button), and you should see the following message in the terminal:

*** Booting MCUboot v2.1.0-rc1-2-g9f034729d99a ***

*** Using Zephyr OS build v3.6.0-4046-gf279a03af8ab ***

I: Starting bootloader

I: Primary image: magic=unset, swap_type=0x1, copy_done=0x3, image_ok=0x3

I: Secondary image: magic=unset, swap_type=0x1, copy_done=0x3, image_ok=0x3

I: Boot source: none

I: Image index: 0, Swap type: none

I: Bootloader chainload address offset: 0x0

I: Jumping to the first image slot

*** Booting Zephyr OS build v3.6.0-4046-gf279a03af8ab ***

Hello World! frdm_mcxn947/mcxn947/cpu0/qspi

Debugging

Here is an example for the Hello World application.

# From the root of the zephyr repository

west build -b frdm_mcxn947/mcxn947/cpu0 samples/hello_world

west debug

Open a serial terminal, step through the application in your debugger, and you should see the following message in the terminal:

*** Booting Zephyr OS build v3.6.0-479-g91faa20c6741 ***

Hello World! frdm_mcxn947/mcxn947/cpu0