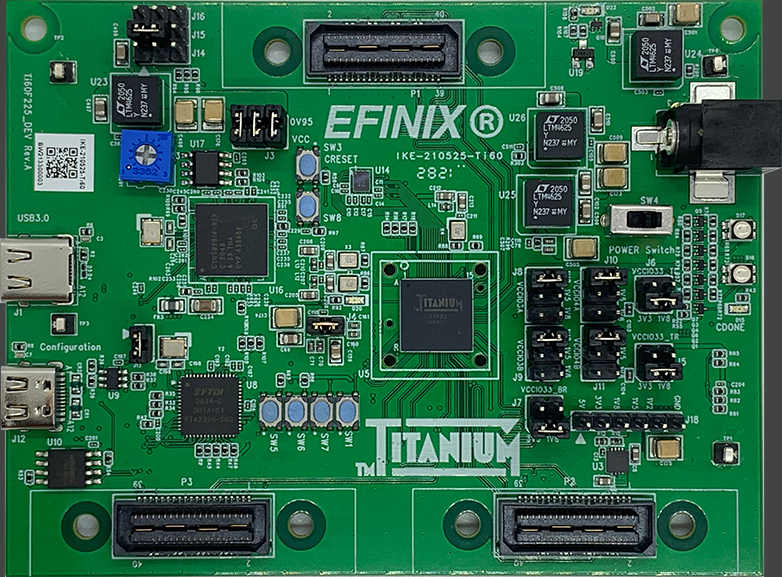

Efinix Titanium Ti60 F225

Overview

The Efinix Titanium Ti60 F225 development kit contains a Ti60 FPGA, which is fabricated on a 16nm process and deliver high performance with the lowest possible power on a small physical size. In addition, Efinix offers Sapphire SoC IP, which is a user-configurable RISC-V SoC based on the VexRiscv core with configurable feature set and extension. Using the Efinity IP Manager, you can configure the SoC to include only the peripherals that you require.

Figure is the development board

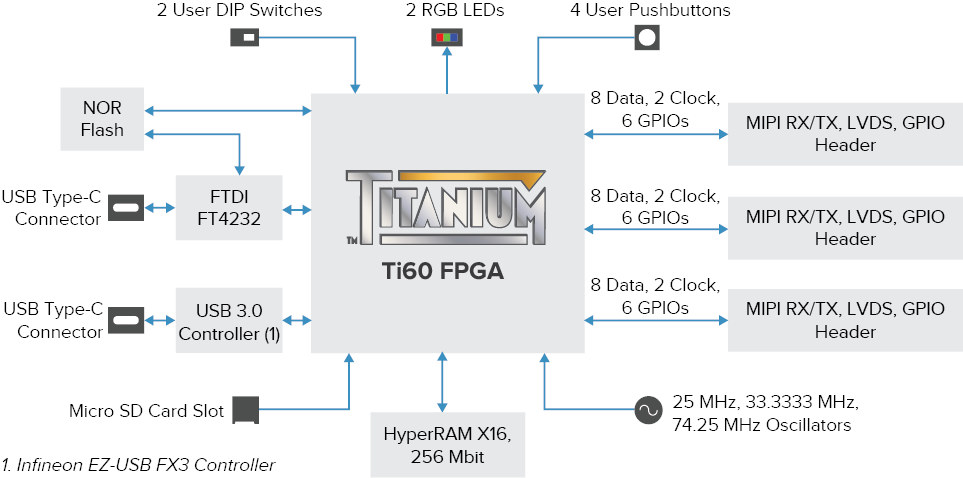

Board block diagram

Sapphire SoC setup on the FPGA guide

Guide to setup the SoC found at Efinix-Zephyr [2]

Building

Build applications as usual (see Building an Application and Run an Application for more details).

# From the root of the zephyr repository

west build -b titanium_ti60_f225 samples/hello_world

Flashing

Flashing the binary into SPI NOR flash requires Efinity programmer, Please find the guide at Efinix-Zephyr [2]

Note

The Zephyr RTOS has been verified using the SoC bitstream generated by Efinity IDE v2022.2.322.