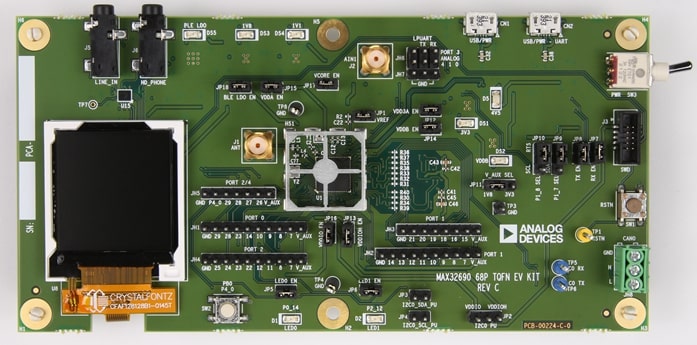

MAX32690EVKIT

Overview

The MAX32690 evaluation kit (EV kit) provides a platform for evaluating the capabilities of the MAX32690 microcontroller, which is an advanced system-on-chip (SoC). It features an Arm® Cortex®-M4F CPU for efficient computation of complex functions and algorithms, and the latest generation Bluetooth® 5 Low Energy (Bluetooth LE) radio designed for wearable and hearable fitness devices, portable and wearable wireless medical devices, industrial sensors/networks, internet of things (IoT), and asset tracking.

The Zephyr port is running on the MAX32690 MCU.

Hardware

MAX32690 MCU:

Ultra-Efficient Microcontroller for Battery-Powered Applications

120MHz Arm Cortex-M4 Processor with FPU

7.3728MHz and 60MHz Low-Power Oscillators

External Crystal Support (32MHz required for BLE)

32.768kHz RTC Clock (Requires External Crystal)

8kHz Always-On Ultra-Low Power Oscillator

3MB Internal Flash, 1MB Internal SRAM (832kB ECC ON)

TBDμW/MHz Executing from Cache at 1.1V

1.8V and 3.3V I/O with No Level Translators

External Flash & SRAM Expansion Interfaces

Bluetooth 5.2 LE Radio

Dedicated, Ultra-Low-Power, 32-Bit RISC-V Coprocessor to Offload Timing-Critical Bluetooth Processing

Fully Open-Source Bluetooth 5.2 Stack Available

Supports AoA, AoD, LE Audio, and Mesh

High-Throughput (2Mbps) Mode

Long-Range (125kbps and 500kbps) Modes

Rx Sensitivity: -97.5dBm; Tx Power: +4.5dBm

Single-Ended Antenna Connection (50Ω)

Multiple Peripherals for System Control

16-Channel DMA

Up To Five Quad SPI Master (60MHz)/Slave (48MHz)

Up To Four 1Mbaud UARTs with Flow Control

Up To Two 1MHz I2C Master/Slave

I2S Master/Slave

Eight External Channel, 12-bit 1MSPS SAR ADC w/ on-die temperature sensor

USB 2.0 Hi-Speed Device

16 Pulse Train Engines

Up To Six 32-Bit Timers with 8mA High Drive

Up To Two CAN 2.0 Controllers

Up To Four Micro-Power Comparators

1-Wire Master

Security and Integrity

ChipDNA Physically Un-clonable Function (PUF)

Modular Arithmetic Accelerator (MAA), True Random Number Generator (TRNG)

Secure Nonvolatile Key Storage, SHA-256, AES-128/192/256

Secure Boot ROM

External devices connected to the MAX32690EVKIT:

Bluetooth SMA Connector with a Hinged 2.4GHz Whip Antenna

3-Pin Terminal Block for CAN Bus 2.0

Selectable On-Board High-Precision Voltage Reference

On-Board HyperRAM

Stereo Audio Codec with Line-In and Line-Out 3.5mm Jacks

128 x 128 (1.45in) Color TFT Display

USB 2.0 Micro-B Interface to the MAX32690

USB 2.0 Micro-B to Serial UART

Board Power Provided by either USB Port

Jumpers to Enable Optional Pull-Up Resistors on I2C port

All GPIOs Signals Accessed through 0.1in Headers

Three Analog Inputs Accessed through 0.1in Headers with Optional Filtering

SWD 10-Pin Header

On-Board 3.3V, 1.8V, and 1.1V LDO Regulators

Individual Power Measurement on All IC Rails through Jumpers

Two General-Purpose LEDs and One GeneralPurpose Push Button Switch

Supported Features

Below interfaces are supported by Zephyr on MAX32690EVKIT.

Interface |

Controller |

Driver/Component |

|---|---|---|

NVIC |

on-chip |

nested vector interrupt controller |

SYSTICK |

on-chip |

systick |

CLOCK |

on-chip |

clock and reset control |

GPIO |

on-chip |

gpio |

UART |

on-chip |

serial |

SPI | on-chip | spi |

||

I2C | on-chip | i2c |

||

TRNG |

on-chip |

entropy |

DMA |

on-chip |

dma controller |

Watchdog |

on-chip |

watchdog |

ADC |

on-chip |

adc |

Timer |

on-chip |

counter |

Connections and IOs

Name |

Name |

Settings |

Description |

||||||

|---|---|---|---|---|---|---|---|---|---|

JP1 |

VREF |

|

|

||||||

JP2 |

I2C0 PU |

|

|

||||||

JP3 |

I2C0_SDA_PU |

|

|

||||||

JP4 |

I2C0_SCL_PU |

|

|

||||||

JP5 |

LED0 EN |

|

|

||||||

JP6 |

LED1 EN |

|

|

||||||

JP7 |

RX EN |

|

|

||||||

JP8 |

TX EN |

|

|

||||||

JP9 |

P1_7 SEL |

|

|

||||||

JP10 |

P1_8 SEL |

|

|

||||||

JP11 |

V_AUX SEL |

|

|

||||||

JP12 |

VDD3A EN |

|

|

||||||

JP13 |

VDDIOH EN |

|

|

||||||

JP14 |

VDDB EN |

|

|

||||||

JP15 |

VDDA EN |

|

|

||||||

JP16 |

VDDIO EN |

|

|

||||||

JP17 |

VCORE EN |

|

|

||||||

JP18 |

BLE LDO EN |

|

|

||||||

JH6 |

ANALOG PORT3 |

|

|

Programming and Debugging

Flashing

The MAX32690 MCU can be flashed by connecting an external debug probe to the SWD port. SWD debug can be accessed through the Cortex 10-pin connector, J3. Logic levels are fixed to VDDIO (1.8V).

Once the debug probe is connected to your host computer, then you can simply run the

west flash command to write a firmware image into flash.

Note

This board uses OpenOCD as the default debug interface. You can also use

a Segger J-Link with Segger’s native tooling by overriding the runner,

appending --runner jlink to your west command(s). The J-Link should

be connected to the standard 2*5 pin debug connector (JW3) using an

appropriate adapter board and cable.

Debugging

Please refer to the Flashing section and run the west debug command

instead of west flash.